xyz f

0 0 0

0 1 0

100

101

1 1 0

0

1

1

0

1

0 0 1 1

0 1 1

# **Homework 1**

(Due date: January 24<sup>th</sup> @ 5:30 pm) Presentation and clarity are very important!

## PROBLEM 1 (25 PTS)

a) Simplify the following functions using ONLY Boolean Algebra Theorems. For each resulting simplified function, sketch the logic circuit using AND, OR, XOR, and NOT gates. (9 pts)

$$\checkmark \quad F = A(C + \bar{B}) + \bar{A} \qquad \qquad \checkmark \quad F = (Y + Z)(\bar{Y} + X) \qquad \qquad \checkmark \quad F(X, Y, Z) = \prod(M_0, M_1, M_4, M_5)$$

b) For the following Truth table: (6 pts)

- Provide the Boolean function using the Canonical Sum of Products (SOP), and Product of Sums (POS).

- Express the Boolean function using the minterms and maxterms representations.

- Sketch the logic circuit as Canonical Sum of Products and Product of Sums.

# PROBLEM 2 (15 PTS)

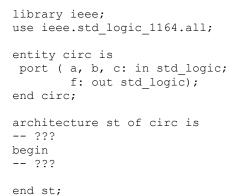

a) Complete the timing diagram of the logic circuit whose VHDL description is shown below: (5 pts)

| library ieee;<br>use ieee.std_logic_1164.all;                                            |   |

|------------------------------------------------------------------------------------------|---|

| <pre>entity circ is    port ( a, b, c: in std_logic;</pre>                               | a |

| <pre>f: out std_logic); end circ;</pre>                                                  | b |

| architecture st of circ is<br>signal x, y: std_logic;<br>begin                           | c |

| <pre>x &lt;= a and b;<br/>y &lt;= x nand c;<br/>f &lt;= y xor (not b);<br/>end st;</pre> | f |

b) The following is the timing diagram of a logic circuit with 3 inputs. Sketch the logic circuit that generates this waveform. Then, complete the VHDL code. (10 pts)

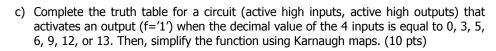

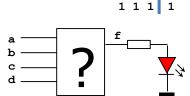

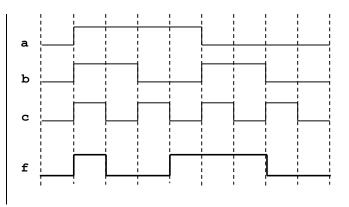

## PROBLEM 3 (10 PTS)

• For the following 4-bit bidirectional port, complete the timing diagram (signals *DO* and *DATA*):

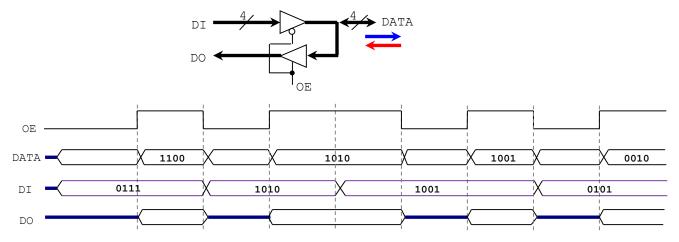

# PROBLEM 4 (10 PTS)

- A 24-bit address line in a  $\mu$ processor handles up to  $2^{24} = 16 MB$  of addresses, each address containing onebyte of information. We want to connect four 4MB memory chips to the  $\mu$ processor.

- Sketch the circuit that: i) addresses the memory chips, and ii) enables only one memory chip (via CE: chip enable) when the address falls in the corresponding range. Example: if address = 0x5FFFFF,  $\rightarrow$  only memory chip 2 is enabled (CE=1). If address = 0xD00FA0,  $\rightarrow$  only memory chip 4 is enabled.

- Complete the number of bits '??' required for each 4MB memory chip.

#### PROBLEM 5 (15 PTS)

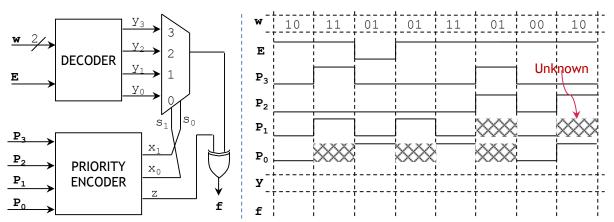

• Complete the timing diagram of the circuit shown below:

## PROBLEM 6 (15 PTS)

- In these problems, you MUST show your conversion procedure.

- a) Convert the following unsigned integer numbers to their binary and hexadecimal representation. (4 pts) 124, 115, 128, 255.

- b) What is the minimum number of bits required to represent: (3 pts)

- ✓ 50,000 colors?

- ✓ 32679 symbols?

- ✓ 65536 memory addresses in a computer?

- c) A microprocessor can handle addresses from  $0 \times 0000$  to  $0 \times 1FFF$ . How many bits do we need to represent those addresses? (2 pts).

- d) Complete the following table. (6 pts)

| Decimal | BCD            | Binary number | Reflective Gray Code |

|---------|----------------|---------------|----------------------|

| 128     |                |               |                      |

|         |                | 10101011      |                      |

|         | 0100 1001      |               |                      |

|         |                |               | 10001001             |

|         |                | 1110010       |                      |

|         | 0110 0011 0001 |               |                      |

## PROBLEM 7 (10 PTS)

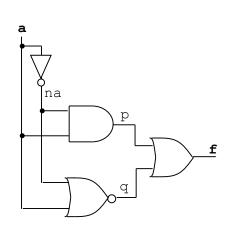

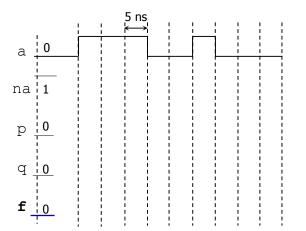

• Complete the timing diagram of the digital circuit shown in the figure below. You must consider the propagation delays. Assume that the propagation delay of every gate is 5 ns. The initial values of the signals are specified in the figure.